AMD: Budoucnost čipů je ve vrstvení

S nástupem 7nm procesu začala AMD využívat čiplety. Ty přinesly několik výhod. Rozdělení čipu na více částí umožnilo jednak zvýšit výtěžnost výroby (výtěžnost klesá exponenciálně s rostoucí plochou monolitického křemíku), snížit výrobní náklady (části čipu, pro které nemá novější = dražší proces smysl lze vyrábět levnější alternativou) a zvýšit výrobní kapacity (využití kapacit GlobalFoundries pro 7nm generaci produktů navzdory tomu, že GlobalFoundries nedisponuje 7nm procesem).

Tyto výhody jsou však vyčerpané, alespoň v ohledu jejich využití pro urychlení vývoje nad rámec možností vývoje výrobních procesů (který je stále pomalejší a jeho mezigenerační posuny stále slabší). Pro samotné zachování náskoku tak AMD potřebuje podniknout další krok, který by přinesl nové výhody.

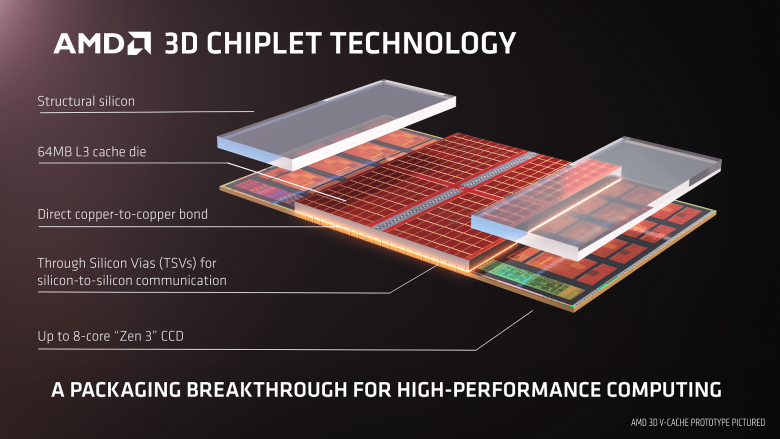

Tím krokem bude vrstvení. Vedle sebe umístěné čiplety mají několik omezujících vlastností. Jednou z nich je rozhraní, kterým jsou propojené. Spoje jsou poměrně dlouhé a rozhraní relativně úzké. To znamená, že datová propustnost mezi čiplety je o několik řádů nižší než datová propustnost na úrovni čipletu a dále v poměru datových přenosů na jednotku spotřeby řádově horší. Protože AMD z nemalé části vyčerpala takové možnosti využití této technologie, pro které nejsou tyto limity příliš omezující, dozrál čas na vrstvení.

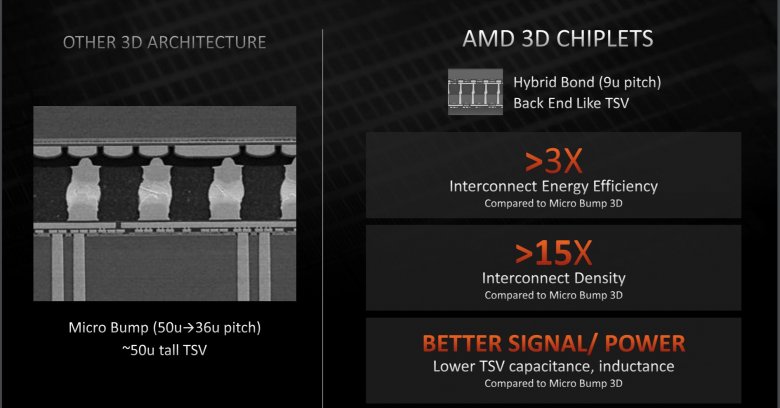

Zatímco u klasických čipletů je pro komunikační rozhraní využíván pouze obvod čipletů (v kombinaci s hrubým rozhraním), v případě vrstvení jde o plochu, navíc s o několik řádů jemnějším rozhraním. Rozteč jednotlivých spojů je podstatně hustší. Protože má počet spojů na plochu podstatný vliv na datovou propustnost rozhraní a jeho energetické nároky (čím vyšší počet spojů, tím lépe), je právě tento ukazatel jedním z klíčových parametrů technologie.

AMD ilustruje rozteče několika rozhraní: C4 se 130 μm, tzv. Micro Bump s 50 μm a vlastním řešením s až 9 μm roztečí. V této souvislosti nebude od věci drobná odbočka:

Jednou z prvních osob, která na tuto novinku upozornila, je redaktor webu Anandtech Ian Cutress:

Ve svém příspěvku na Twitteru srovnává 9μm údaj AMD s 10μm hodnotou, která podle jeho slov platí pro pouzdření Intel Foveros. Pokud se však podíváme na slajd Intelu, ve které v roce 2018 plány s technologií Foveros představil, neuváděl hodnotu 10 μm, ale podstatně hrubších 36 μm:

Později Intel upřesnil, že stávající Foveros používá 50μm rozteč spojů. Na 36μm přejde až ve druhé polovině roku 2022.

Loni (2020) pak ohlásil přípravu nové generace Foverosu s 25μm roztečí a budoucí výhled na <10μm rozteč:

Letos nazval budoucí 25μm Foveros jako Foveros Omni a <10μm Foveros jako Foveros Direct:

Těžko tedy říct, proč Cutress srovnává technologii AMD, která bude zanedlouho dostupná na trhu, s technologií Intelu dostupnou v horizontu několika let. Zatímco AMD se s využitím externího partnera (TSMC) dostane letos pod 20μm hranici, Intel s takovým řešení přijde až ve druhé polovině roku 2023. Ve snaze vysvětlit, proč Cutress se soudobou technologií AMD nesrovnává soudobou technologii Intelu, ale 2-3 roky vzdálený výhled, by se nabízela možnost, že se přehlédl a nevšiml, že 10μm údaj Intelu se týká vzdálené budoucnosti. Což je však v rozporu s faktem, že sám sestavil tabulku technologií Intelu, ve které správně <10μm technologii Intelu uvedl do druhého pololetí 2023 a detailně rozepsal, ve kterém kvartálu plánuje Intel nasadit kterou verzi:

Vraťme se k plánům AMD, byť i ty pokračují srovnáním:

Ukazují totiž, že oproti technologii Micro Bumps, která dosahuje / dosáhne rozteče 50-36 μm a kde jsou spoje vysoké kolem 50 μm, jsou měděné spoje v případě řešení AMD v přímém kontaktu (bez tohoto 50μm zvýšení) a díky >15× vyšší hustotě spojů dosahují >3× vyšší energetické efektivity.

Na celé situaci jsou překvapivé hlavně dva aspekty. Tím prvním je fakt, že se AMD podařilo s využitím externího dodavatele (TSMC), který má na starosti i řadu jiných firem a jejich projektů připravit řešení pokročilejší než Intelu, který má vlastní továrny a vlastní vývoj sám pro své potřeby a účely. Druhým pak je skutečnost, že Intel k současnému období již tři roky hovoří o pokročilém pouzdření Foveros, ale za tuto dobu vydal jediný produkt tuto technologii využívající (Lakefield), který dokázal přinést asi o 10 % vyšší výkon než soudobý Atom při asi 5× vyšší ceně (čemuž odpovídalo reálné rozšíření na trhu).

Naproti tomu AMD o podobných řešeních donedávna jen mlčela, poté předvedla Ryzen s V-cache, který má být již koncem roku dostupný a nakonec vyplývá na povrch, že její řešení dosahuje technologické úrovně, kterou má Intel nabídnout až ve druhém pololetí roku 2023.